Hot Chips 2025: Flüssigkühlungsinnovationen für den KI-Boom

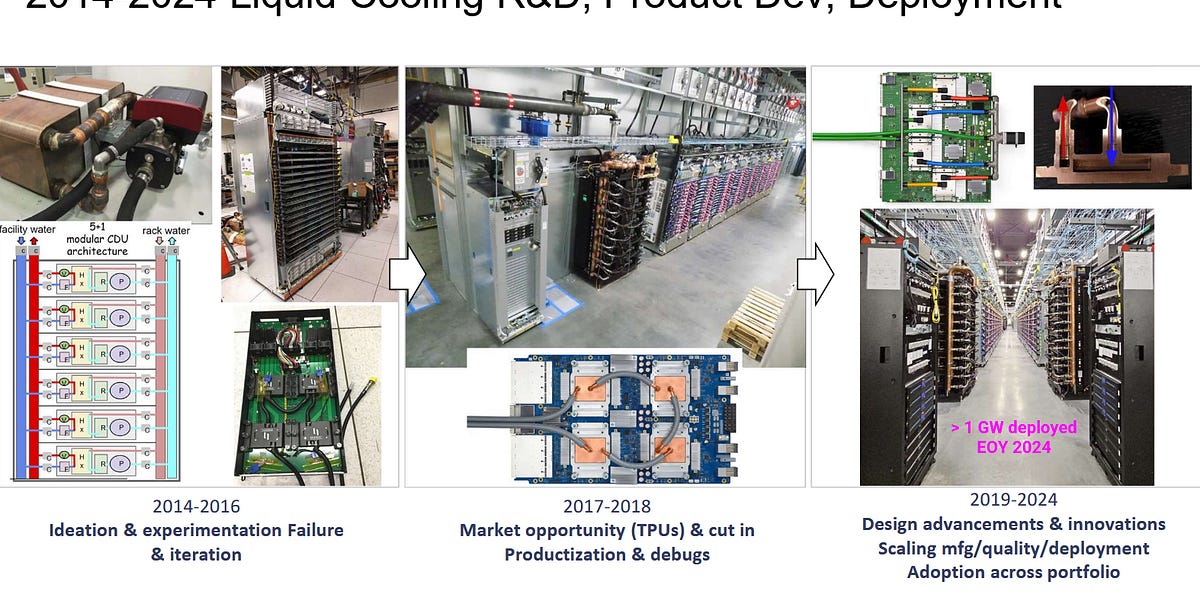

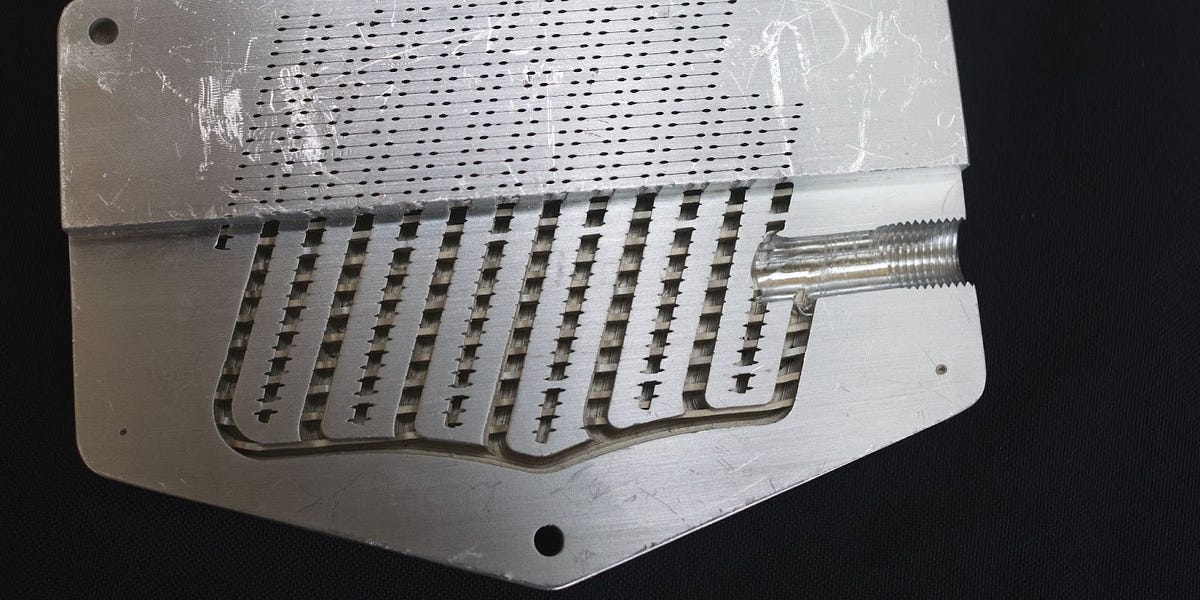

Hot Chips 2025 zeigte fortschrittliche Flüssigkühltechnologien, die auf KI-Chips zugeschnitten sind. Anbieter präsentierten verschiedene Kaltplatten mit Mikrojets, die Hotspots auf Chips präzise kühlen können, sogar durch direkte Wasserinjektion auf den Die. Derzeit konzentriert sich dies auf Serveranwendungen, aber die präzise Temperaturregelung bietet zukünftig Potenzial für Consumer-Hardware. Die Ausstellung zeigte auch Kaltplatten aus verschiedenen Materialien, wie leichtem Aluminium und hocheffizientem Kupfer, um unterschiedliche Gewichts- und Kühlanforderungen von Servern zu erfüllen. Angesichts des stetig steigenden Energieverbrauchs und der Wärmeabfuhr von KI-Chips werden diese Flüssigkühlungsinnovationen zu entscheidenden Lösungen für die Kühlung von Rechenzentren.

Mehr lesen